東芝は、高いキャリア移動度と薄い等価酸化膜厚を両立でき16nm世代以降のLSIに用いられる金属絶縁膜半導体型(MIS)トランジスタに適用可能な新しいゲート絶縁膜積層技術を開発した。

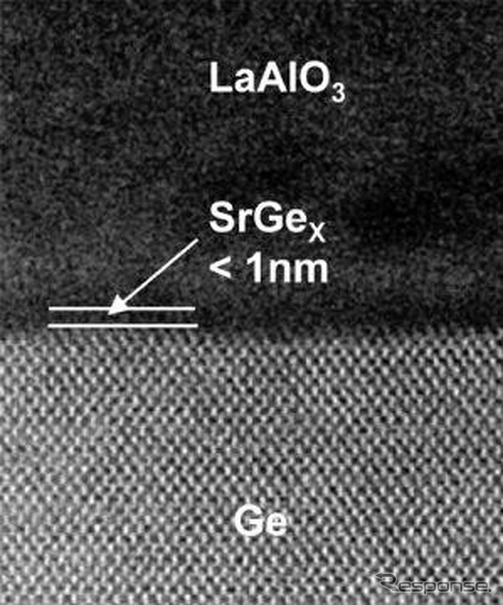

今回開発した技術は、高誘電率ゲート絶縁膜と、ゲルマニウムチャネルとの間に、「ストロンチウムジャーマナイド」界面層を挿入するプロセス技術で、これにより高いキャリア移動度と、ゲート絶縁膜積層構造の薄膜化の両立を可能とした。

具体的なプロセスは、まず超高真空中のゲルマニウム表面を加熱により清浄化する。その上に、数原子層程度のストロンチウムを堆積し、さらに高誘電率絶縁膜層である「ランタンアルミネート」層を形成した後、窒素ガス中で熱処理を行う。

これらの工程の中で、ストロンチウムとゲルマニウムが反応し、「ストロンチウムジャーマナイド」層が形成される。

このプロセスを用いたトランジスタの正孔移動度は、高誘電率ゲート絶縁膜を用いたゲルマニウムpMISトランジスタとしては世界最高の481平方センチ/Vspec(ピーク時を実現した。これはストロンチウムジャーマナイド層が無い場合の3倍以上で、シリコンで実現可能な正孔移動度の2倍以上となる。

加えてストロンチウムジャーマナイド界面層の薄膜化についても実証した。今回の成果は、6月15日から京都市で開催中のVLSIシンポジウムで発表する。